Araştırma

Araştırmalarımızın amacı, elektronik devre ve sistemler için hesaplama, devre tasarımı ve güvenilirlik konularında yeni yaklaşımlar geliştirmektir. Araştırmalarımız temelde yeni ve gelişen teknolojileri ve hesaplama düzenlerini hedef almaktadır. Aşağıda en yeniden en eskiye ve önem sırasına göre sıralanan araştırma konuları yer almaktadır. Her konu kısaca anlatılmış ve ilgili yayın ve projeler eklenmiştir.

Contents |

Nano-Çaprazlayıcı Dizinler ile Hesaplama | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

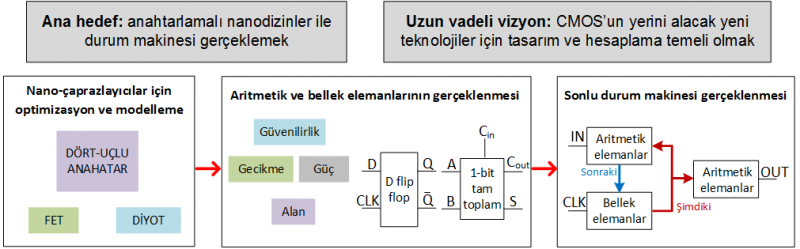

Nano-çaprazlayıcı dizinler gelecekte CMOS'un yerini alabilecek önemli teknolojilerden biridir. Nano dizinler düzenli ve sık yapılardır; üretimlerinde CMOS'tan farklı olarak sadece litografi gibi karmaşık yöntemler kullanılmaz; Bunun yanı sıra kendiliğinden üretime (self-assembly) dayanan teknikler de kullanılır. Günümüzde nano dizinler, her bir çaprazlayıcısı (crosspoint) diyot, FET veya anahtar olarak çalışacak şekilde üretilebilmekte ve bu da bu geleneksel devre elemanları için geliştirilmiş olan devre tasarım tekniklerini kullanmamıza olanak sağlamaktadır. Buradan yola çıkarak, nano ahtarlamalı dizinler için komple bir sentez ve performans optimizasyon metodolojisi geliştirmeyi hedefliyoruz. Çalışmalarımızın yeni gelişen CMOS sonrası bilgisayarların gerçeklenmesinde önemli bir gelişme olacağını düşünüyoruz.

SentezBoolean fonksiyonları diyot, FET ve dört-uçlu anahtar tabanlı nano dizinler ile gerçekledik ve dizin boyut formülleri elde ettik. Buna ek olarak, dört-uçlu anahtarlardan oluşan dizinleri optimum sentezleyen bir algoritma geliştirdik. Hata ToleransıYeniden ayarlanabilir nano dizinlerde oluşan açık ve kapalı hataları inceledik. Kalıcı hatalar için, sıralama, geri-izleme ve satır eşleştirme tekniklerini kullanan hızlı bir buluşsal algoritma geliştirdik. Yumuşak/geçici hatalar için, tolere edilebilir bütün hata yerlerini yinelemeli bir teknik kullanarak belirledik.

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Tersinir Devre Tasarımı ve CMOS Dönüşümü | ||||||||||||||||||||||||||||||||||||||||||

|

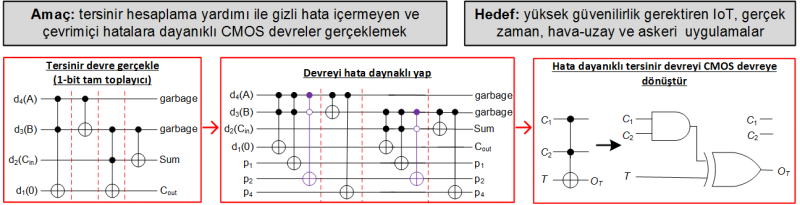

Geleneksel CMOS devrelerinden farklı olarak, tersinir devreler gizli hatalara sahip değildir, bu nedenle dahili devre düğümlerinde meydana gelen hatalar her zaman çıkışta bir hataya neden olur. Bu, çevrimiçi veya eşzamanlı hata toleransı için eşsiz bir özelliktir. Bu durumdan hareketle, tersinir hesaplamayı kullanarak hataya dayanıklı CMOS devre blokları gerçekliyoruz. Öncelikle tersinir kapılarla tersinir devreler sentezliyoruz; sonra onları hataya dayanıklı hale getiriyoruz; ve son olarak tersinir kapılardan CMOS kapılara dönüşümü yapıyoruz.  SentezTersinir Boolean fonksiyonları kuantum kapılar ile gerçekleyen hızlı bir algoritma önerdik. Önerdiğimiz algoritma, her bir fonksiyon için zaman alıcı bir arama yapmak yerine temel fonksiyonları kullanmaktadır ve sonrasında sıralama yapmaktadır. Örnek vermek gerekirse, toplamda 20922789888000 fonksiyonun olduğu 4 bit devrelerdeki temel fonksiyon sayısı yalnızca 120'dir. Buna ek olarak, komşu kapı çiftlerini göz önüne alarak tersinir ve kuantum devre masraflarını optimize ettik. Çevrimiçi Hata Tespiti ve DüzeltmeÇoklu kontrol Toffoli kapılarını kullanarak tersine çevrilebilir bir devrede hataya dayanıklı hale getirmek için iki teknik geliştiriyoruz. İlk olarak, tek parite korumasına dayanan ve çıktıdaki tek sayıdaki hataları tespit edebilen bir teknik geliştirdik. İkinci teknik ise Hamming kodları üzerine inşa edilen bir hata düzeltme tekniğidir. Aynı zamanda, Fredkin kapısı gibi korunumlu tersinir kapılarla mükemmel hata tespitinin mümkün olduğunu gösterdik. Bir sonraki adım olarak, önerilen tersinir devreleri geleneksel CMOS kapılarından oluşan devrelere dönüştürdük.

| ||||||||||||||||||||||||||||||||||||||||||

Stokastik Devre Tasarımı | ||||||||||||||||||||||||||||||||

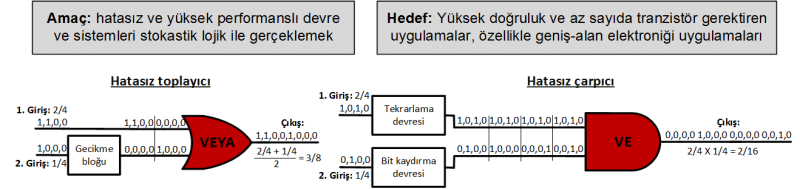

Yüksek Doğruluklu Aritmetik GerçeklemelerStokastik hesaplamanın en önemli sorunu düşük doğruluk veya bununla ilişkili olarak uzun hesaplama süreleridir. Bu soruna, bit katarlarını geri besleme mekanizmalarının da yardımıyla manipüle ederek bir çözüm bulduk. Alan, gecikme ve doğruluk parametrelerini göz önüne alarak hatasız çalışan toplayıcı ve çarpıcı devreler gerçekledik.

| ||||||||||||||||||||||||||||||||

Yaklaşık Devre ve Sistem Tasarımı | |||||||||||||||||||||||||

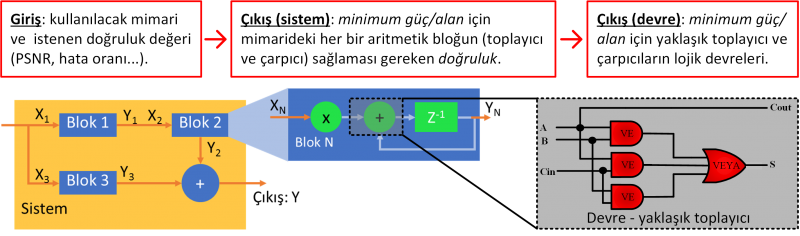

Güç Verimli Yaklaşık Sistem Tasarım MetodolojisiBu çalışmanın amacı, sistemin performans kriterlerini en iyi şekilde karşılamak için yaklaşık hesaplama bloklarının nasıl seçileceğini bulmaktır. Yaklaşık hesaplama bloklarının sistematik olarak kullanılmasıyla, maksimum güç tasarrufu elde edilebilir. Önerilen metodoloji herhangi bir dijital teknoloji için uygulanabilirdir. Yöntem, her bloğun yeterli çıktı kalitesini belirlemek için toplam sistemi en üst seviyeden aritmetik birimlerine kadar araştırır.

| |||||||||||||||||||||||||

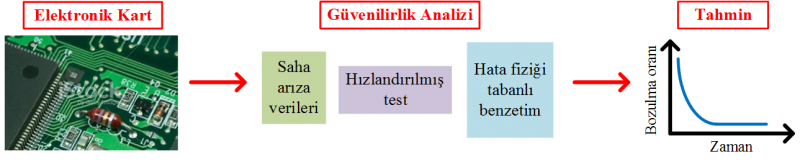

Elektronik Ürünlerin Güvenilirliği | |

|

Elektronik sektöründe yaşanan baş döndürücü gelişmeler, elektronik devre ve sistemlerin güvenilirliği kavramını yeniden şekillendirmiştir. Elektronik ürünlerin günümüzdeki hızlı üretim döngüleri, uzun süreli ve masraflı olan geleneksel hızlandırılmış testlerin öneminin azalmasına neden olmuştur. Biz bu çalışmada görece masrafsız ve yüksek doğruluklu bir güvenilirlik analizi metodolojisi önerdik. Bu noktada saha verileri, yeni hızlandırılmış testler ve hata fiziği tabanlı benzetimlerden yararlandık. Çalışmalarımız Avrupa'nın en büyük ev aletleri ve beyaz eşya üreticilerinden biri olan Arçelik A.Ş. ile birlikte yürütülmüştür.  Saha Verileri ile Güvenilirlik Analizi ve TahminiYüksek miktarda üretilen elektronik ürünler için saha arıza verileri ile güvenilirlik tahmin modeli geliştirdik. Modelimizi, önerdiğimiz değişim noktası tespit metodunu kullanarak Weibul-eksponansiyel dağılımı üzerine inşa ettik. Modelimiz, elektronik kartların kısa süreli saha verilerini kullanarak, garanti süresi içerisindeki güvenilirlik performanslarını yüksek doğrulukta tahmin etmektedir. Bu çalışmada kullandığımız kartların garanti süresi 3 yıldır ve kullandığımız veri seti 3 aylıktır. Varistörlerin Bozunum ProsesleriZnO varistörlerde görülen değişik bozunum mekanizmalarını inceledik. Varistör voltajı Vv'nin değişik stres seviyelerinde nasıl değiştiğini modelledik. Bu amaç için, değişik AC akımlar kullanarak hızlandırılmış testler uyguladık ve Vv değerlerini ölçtük. Literatürdeki genel kanının aksine sadece düşen Vv değerleri değil, yükselen Vv değerleri de gözlemledik. Kalibreli Hızlandırılmış TestlerElektronik ürünlerin hata oranlarındaki önemli azalma, geleneksel ALT (accelerated life tests) kullanımını oldukça masraflı ve zaman alıcı bir hale getirmiştir. Bu aşamada yeni bir test metodolojisi olan CALT (calibrated accelerated life tests) önerilmiştir. Bu çalışmada, ALT ve CALT testlerini detaylı olarak karşılaştırdık; hata oranı, hızlandırma faktörü ve stres seviyesinin test süresine olan etkilerini inceledik. | |

Analog Devre Tasarımı | |||||||||||||||

Pozitif GeribeslemeGeleneksel olarak analog devreler pozitif geribesleme çevrimleri içermemelidirler. Aykırı gözükse de, biz bu çalışmada akım kuvvetlendiricilerin giriş empedanslarını pozitif geribesleme kullanarak başarıyla iyileştirdik. Ek olarak yeni bir tamamen farksal akım kuvvetlendirici devresi önerdik ve bu devreyi filtre uygulamalarında test ettik.

| |||||||||||||||

Ayrık Matematik | |||||||||||||

"Self Duality" ProblemiIDNF (irredundant disjuntive normal form) formundaki monoton bir Boolean fonksiyonun self-dual olup olmadığının zaman karmaşıklığında belirlenmesi, matematikte çözülememiş önemli problemlerden biridir. Bu çalışma bu ünlü problem üzerinedir. Biz bu çalışmada IDNF formundaki monoton Boolean fonksiyonların değişken sayısının çarpım (disjunct) sayısından fazla olamayacağını gösterdik. Ayrıca n sayıda çarpım ve n sayıda değişken içeren IDNF formundaki monoton Boolean fonksiyonların, self-dual olup olmadığını bulan bir algoritma geliştirdik. Algoritmanın zaman karmaşıklığı O(n^3)'dür.

| |||||||||||||