Araştırma

| (35 intermediate revisions by one user not shown) | |||

| Line 7: | Line 7: | ||

{| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | {| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | ||

|- | |- | ||

| − | | colspan="2" style="background:# | + | | colspan="2" style="background:#8FBCBF; text-align:center; padding:1px; border-bottom:1px #8FBCBF solid;" | |

| + | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Anahtarlamalı Kafesler ile Hesaplama </h2> | ||

| + | |||

| + | |- | ||

| + | | valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | ||

| + | |||

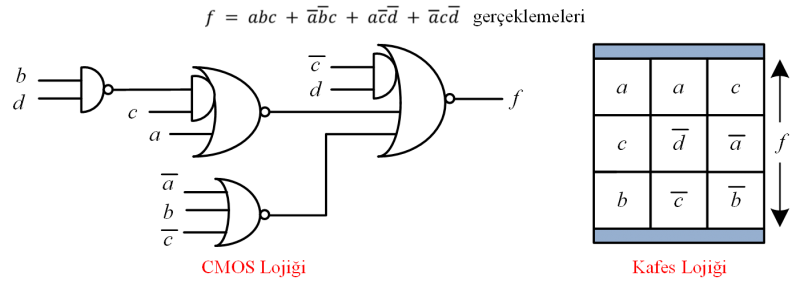

| + | Dört uçlu anahtarlardan oluşan iki boyutlu bir ağ olarak oluşturulan anahtarlamalı kafes, lojik hesaplama için düzenli, yoğun, alan verimli ve CMOS uyumlu bir yapı olarak sunulmuştur. Kafesin her bir bölümü dört uçlı bir anahtardır ve bir kontrol girişine ve dört terminale sahiptir. Kontrol girişi, tüm terminallerinin bağlantılarını keser (KAPALI) veya tümünün bağlı (AÇIK) olmasını sağlar. | ||

| + | |||

| + | [[Image:arastirma_lattice_logic.png|center|none|800px|link=]] | ||

| + | |||

| + | <h3> | ||

| + | Teknoloji Geliştirme</h3> | ||

| + | |||

| + | Anahtarlamalı kafeslerinin '''CMOS uyumlu''' olduğunu gösterdik. Bu amaçla, farklı dört uçlu anahtar yapıları önerdik; bunları üç boyutlu teknoloji bilgisayar destekli tasarım (TCAD) ortamında, TSMC 65nm CMOS prosesinin tasarım kurallarını karşılayarak, ve ayrıca Cadence ortamında kurduk ve simülasyonlarını tamamladık. Deneysel sonuçlar, anahtarlamalı kafesleri kullanılarak lojik fonksiyonları gerçeklemenin, geleneksel CMOS gerçeklemeleri ile karşılaştırıldığında '''çok daha az serim alanı kapladığını''' ve rekabetçi gecikme ve güç tüketimi değerlerine sahip olduğunu göstermektedir. | ||

| + | |||

| + | [[Image:arastirma_lattice_technology.png|center|none|800px|link=]] | ||

| + | |||

| + | <h3> | ||

| + | Performans Optimizasyonu</h3> | ||

| + | '''Gecikme kısıtlaması''' altında kafes boyutlarını optimize etmek için bir lojik sentez algoritması önerdik. Ayrıca kafeslerin '''alan-gecikme-güç verimliliği için statik ve dinamik lojik çözümleri''' önerdik. | ||

| + | <!-- [[Image:Research-2.png|center|none|800px|link=]] --> | ||

| + | |||

| + | <h3> | ||

| + | Sentez</h3> | ||

| + | Minimum boyutta anahtarlama kafesler ile lojik fonksiyonları gerçeklemek için '''optimum ve sezgisel algoritmalar''' önerdik. | ||

| + | |||

| + | <!-- [[Image:Research-1.png|center|none|800px|link=]] --> | ||

| + | |||

| + | <!-- YAYIN --> | ||

| + | {| id="mp-upper" style="width: 100%; margin:4px 0 0 0; background:none; border-spacing: 0px;" | ||

| + | | class="MainPageBG" style="width:50%; border:0px solid #D8BFD8; vertical-align:top; color:#000;" | | ||

| + | {| id="mp-left" style="width:100%; vertical-align:top;" | ||

| + | |||

| + | | | ||

| + | |||

| + | {| style="border:1px solid #abd5f5; background:#d0e5f5; padding:0.2em 0.5em; font-weight:bold;" | ||

| + | |||

| + | |- valign=top | ||

| + | | width="696" |'''Seçilmiş Yayınlar''' | ||

| + | |} | ||

| + | |||

| + | {| style="border:1px solid #abd5f5; background:#f1f5fc;" | ||

| + | |||

| + | | | ||

| + | {| | ||

| + | |- valign=top | ||

| + | | width="100" |'''başlık''': | ||

| + | | width="450"|[[Media: Akkan_EtAl_H_and_Square_Lattice_Technology_Development.pdf | Technology Development and Modeling of Switching Lattices Using Square and H Shaped Four-Terminal Switches]] | ||

| + | |- valign="top" | ||

| + | | '''yazarlar''': | ||

| + | | width="450"| Nihat Akkan, Serzat Safaltin, Levent Aksoy, Ismail Cevik, Herman Sedef, Csaba Andras Moritz ve [[Mustafa Altun]] | ||

| + | |- valign="top" | ||

| + | | '''makale''': | ||

| + | | width="450" | [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6245516 IEEE Transactions on Emerging Topics in Computing], Vol. 10, Issue 1, pp. 351–360, 2022. | ||

| + | |- valign=top | ||

| + | | '''bildiri''': | ||

| + | | width="450"| [http://www.date-conference.com/ Design, Automation and Test in Europe (DATE)], Grenoble, France, 2020. | ||

| + | |} | ||

| + | |||

| + | | align=center width="70" | | ||

| + | <span class="plainlinks"> | ||

| + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/6/69/Akkan_EtAl_H_and_Square_Lattice_Technology_Development.pdf]]</span> | ||

| + | <br> | ||

| + | [[Media:Akkan_EtAl_H_and_Square_Lattice_Technology_Development.pdf | Yayın]] | ||

| + | | align="center" width="70" | | ||

| + | <span class="plainlinks"> | ||

| + | |||

| + | [[File:PPT.jpg|60px|link=https://www.ecc.itu.edu.tr/images/1/1c/Cevik_Aksoy_Altun_CMOS_Implementation_of_Switching_Lattices.pptx]] | ||

| + | </span> | ||

| + | <br> [https://www.ecc.itu.edu.tr/images/1/1c/Cevik_Aksoy_Altun_CMOS_Implementation_of_Switching_Lattices.pptx Sunum] | ||

| + | |} | ||

| + | |||

| + | {| style="border:1px solid #abd5f5; background:#f1f5fc;" | ||

| + | | | ||

| + | {| | ||

| + | |- valign=top | ||

| + | | width="100" |'''başlık''': | ||

| + | | width="450"|[[Media:Aksoy_Altun_Realizations_with_Switching_Lattices.pdf | Novel Methods for Efficient Realization of Logic Functions Using Switching Lattices]] | ||

| + | |- valign="top" | ||

| + | | '''yazarlar''': | ||

| + | | Levent Aksoy ve [[Mustafa Altun]] | ||

| + | |- valign="top" | ||

| + | | '''makale''': | ||

| + | | width="450" | [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=12 IEEE Transactions on Computers], Vol. 69, Issue 3, pp. 427–440, 2020. | ||

| + | |- valign="top" | ||

| + | | '''bildiri''': | ||

| + | | width="450"| [http://www.date-conference.com/ Design, Automation and Test in Europe (DATE)], Florence, Italy, 2019. | ||

| + | |} | ||

| + | | align=center width="70" | | ||

| + | <span class="plainlinks"> | ||

| + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/e/e0/Aksoy_Altun_Realizations_with_Switching_Lattices.pdf]]</span> | ||

| + | <br> | ||

| + | [[Media:Aksoy_Altun_Realizations_with_Switching_Lattices.pdf | Yayın]] | ||

| + | | align="center" width="70" | | ||

| + | <span class="plainlinks"> | ||

| + | |||

| + | [[File:PPT.jpg|60px|link=https://www.ecc.itu.edu.tr/images/5/54/Aksoy_Altun_SAT_based_Synthesis_of_Switching_Lattices.pptx]] | ||

| + | </span> | ||

| + | <br> [https://www.ecc.itu.edu.tr/images/5/54/Aksoy_Altun_SAT_based_Synthesis_of_Switching_Lattices.pptx Sunum] | ||

| + | |} | ||

| + | |||

| + | |} | ||

| + | | style="border:1px solid transparent;" | | ||

| + | <!-- PROJE --> | ||

| + | | class="MainPageBG" style="width:50%; border:0px solid #A9A9A9; vertical-align:top;"| | ||

| + | {| id="mp-right" style="width:100%; vertical-align:top;" | ||

| + | | | ||

| + | |||

| + | {| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#d0e5f5; padding:0.2em 0.5em; font-weight:bold;" | ||

| + | |||

| + | |- valign=top | ||

| + | | width="696" |'''Proje Desteği''' | ||

| + | |} | ||

| + | {| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#f1f5fc;" | ||

| + | |||

| + | | | ||

| + | {| | ||

| + | |- valign="top" | ||

| + | | width="140" |'''başlık''': | ||

| + | | width="558"| Anahtarlamalı Kafesler ile Hesaplama: Teknoloji Geliştirme, Eleman Modelleme ve Devre Tasarımı | ||

| + | |- valign="top" | ||

| + | | '''kurum & program''': | ||

| + | | width="450"| [https://h2020.org.tr/tr/content/tubitak-ulusal-bilim-vakfi-nsf-ikili-isbirligi-destek-programi TUBITAK-NSF İkili İşbirliği Programı (2501)] | ||

| + | |- valign="top" | ||

| + | | '''bütçe''': | ||

| + | | 720.000 TL | ||

| + | |- valign="top" | ||

| + | | '''süre''': | ||

| + | | 2019-2023, ''tamamlandı'' | ||

| + | |} | ||

| + | {| style="margin-left: auto; margin-right: 0px; border:0.1px solid #abd5ff; background:#f1f5fc; padding:0.2em 0em;" | ||

| + | |- valign="top" | ||

| + | | width="140" |'''proje hedefi''': | ||

| + | | width="558"| Anahtarlamalı kafes yapılarına dayanan, CMOS uyumlu, ve geleneksel CMOS devrelerine göre çok daha düşük alan kaplayan yeni bir teknoloji geliştirmek ve geliştirilen teknoloji için eksiksiz bir elektronik tasarım otomasyon (Electronic Design Automation – EDA) metodolojisi sunmak. | ||

| + | |} | ||

| + | |} | ||

| + | |||

| + | |} | ||

| + | |} | ||

| + | |} | ||

| + | |||

| + | |||

| + | {| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | ||

| + | |- | ||

| + | | colspan="2" style="background:#8FBCAF; text-align:center; padding:1px; border-bottom:1px #8FBCAF solid;" | | ||

| + | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Enerji Verimli YSA Donanım gerçeklemesi </h2> | ||

| + | |- | ||

| + | | valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | ||

| + | |||

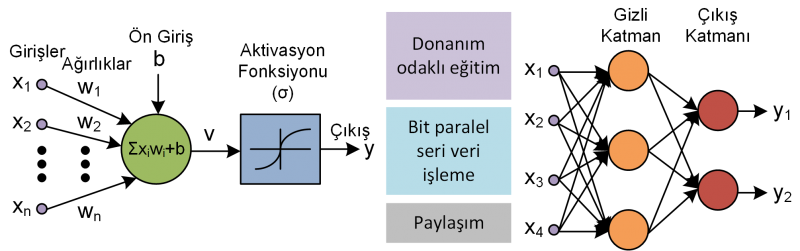

| + | İleri beslemeli yapay sinir ağlarının (YSA) enerji tüketimini azaltmak için '''donanıma odaklı eğitim''' tekniklerini, yeni '''hibrit bit paralel seri''' sayı temsillerini ve sabit çarpma tabanlı '''paylaşım''' tekniklerini kullanmayı amaçlıyoruz. | ||

| + | |||

| + | [[Image:arastirma_ANN.png|center|none|800px|link=]] | ||

| + | |||

| + | |||

| + | <!-- YAYIN --> | ||

| + | {| id="mp-upper" style="width: 100%; margin:4px 0 0 0; background:none; border-spacing: 0px;" | ||

| + | | class="MainPageBG" style="width:50%; border:0px solid #D8BFD8; vertical-align:top; color:#000;" | | ||

| + | {| id="mp-left" style="width:100%; vertical-align:top;" | ||

| + | |||

| + | | | ||

| + | |||

| + | {| style="border:1px solid #abd5f5; background:#d0e5f5; padding:0.2em 0.5em; font-weight:bold;" | ||

| + | |||

| + | |- valign=top | ||

| + | | width="696" |'''Seçilmiş Yayınlar''' | ||

| + | |} | ||

| + | {| style="border:1px solid #abd5f5; background:#f1f5fc;" | ||

| + | | | ||

| + | {| | ||

| + | |- valign=top | ||

| + | | width="100" |'''başlık''': | ||

| + | | width="450"| [[Media:Aksoy_Parvin_Nojehdeh_Altun_Time_Multiplexed_ANN_Implementation.pdf | Efficient Time-Multiplexed Realization of Feedforward Artificial Neural Networks]] | ||

| + | |- valign="top" | ||

| + | | '''yazarlar''': | ||

| + | | Levent Aksoy, Sajjad Parvin, Mohammadreza Nojehdeh ve [[Mustafa Altun]] | ||

| + | |- valign="top" | ||

| + | | '''bildiri''': | ||

| + | | width="450"| [http://iscas2020.org/ IEEE International Symposium on Circuits and Systems (ISCAS)], Seville, Spain, 2020. | ||

| + | |} | ||

| + | | align=center width="70" | | ||

| + | <span class="plainlinks"> | ||

| + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/e/eb/Aksoy_Parvin_Nojehdeh_Altun_Time_Multiplexed_ANN_Implementation.pdf]]</span> | ||

| + | <br> | ||

| + | [[Media:Aksoy_Parvin_Nojehdeh_Altun_Time_Multiplexed_ANN_Implementation.pdf | Yayın]] | ||

| + | | align="center" width="70" | | ||

| + | <span class="plainlinks"> | ||

| + | |||

| + | [[File:PPT.jpg|60px|link=https://www.ecc.itu.edu.tr/images/3/3a/Aksoy_Parvin_Nojehdeh_Altun_Time_Multiplexed_ANN_Implementation.pptx]] | ||

| + | </span> | ||

| + | <br> [https://www.ecc.itu.edu.tr/images/3/3a/Aksoy_Parvin_Nojehdeh_Altun_Time_Multiplexed_ANN_Implementation.pptx Sunum] | ||

| + | |} | ||

| + | |} | ||

| + | |||

| + | | style="border:1px solid transparent;" | | ||

| + | <!-- PROJE --> | ||

| + | | class="MainPageBG" style="width:50%; border:0px solid #A9A9A9; vertical-align:top;"| | ||

| + | {| id="mp-right" style="width:100%; vertical-align:top;" | ||

| + | |||

| + | | | ||

| + | |||

| + | {| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#d0e5f5; padding:0.2em 0.5em; font-weight:bold;" | ||

| + | |||

| + | |- valign=top | ||

| + | | width="696" |'''Proje Desteği''' | ||

| + | |} | ||

| + | |||

| + | {| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#f1f5fc;" | ||

| + | |||

| + | | | ||

| + | {| | ||

| + | |- valign="top" | ||

| + | | width="140" |'''başlık''': | ||

| + | | width="558"|Çok Düşük Enerji Tüketen Taşınabilir Kullanıma Uygun Yapay Sinir Ağlarının (YSA) Donanım Gerçeklemeleri | ||

| + | |- valign="top" | ||

| + | | '''kurum& program''': | ||

| + | | [http://www.tubitak.gov.tr/tr/destekler/akademik/ulusal-destek-programlari/icerik-1001-bilimsel-ve-teknolojik-arastirma-projelerini-destekleme-pr TÜBİTAK Bilimsel ve Teknolojik Araştırma Projelerini Destekleme Programı (1001)] | ||

| + | |- valign="top" | ||

| + | | '''bütçe''': | ||

| + | | 400.000 TL | ||

| + | |- valign="top" | ||

| + | | '''süre''': | ||

| + | | 2020-2023, ''tamamlandı'' | ||

| + | |} | ||

| + | {| style="margin-left: auto; margin-right: 0px; border:0.1px solid #abd5ff; background:#f1f5fc; padding:0.2em 0em;" | ||

| + | |- valign="top" | ||

| + | | width="140" |'''proje hedefi''': | ||

| + | | width="558"| Sayı sistemlerinden başlanarak lojik, devre ve sistem gerçekleme seviyelerinde enerji optimizasyonu yapmak. | ||

| + | |||

| + | |} | ||

| + | |} | ||

| + | <!-- {| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#f1f5fc;" | ||

| + | |||

| + | | | ||

| + | {| | ||

| + | |- valign=top | ||

| + | | width="140" |'''title''': | ||

| + | | width="558"| Gate and Transistor Implementations of Accurate Arithmetic Operation Blocks with Stochastic Logic | ||

| + | |- valign="top" | ||

| + | | '''agency & program''': | ||

| + | | [http://bap.itu.edu.tr/ Istanbul Technical University Research Support Program (ITU-BAP)] | ||

| + | |- valign="top" | ||

| + | | '''duration''': | ||

| + | | 2017-2019 | ||

| + | |} | ||

| + | |||

| + | |} --> | ||

| + | |} | ||

| + | |} | ||

| + | |} | ||

| + | |||

| + | |||

| + | {| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | ||

| + | |- | ||

| + | | colspan="2" style="background:#8FBC9F; text-align:center; padding:1px; border-bottom:1px #8FBC9F solid;" | | ||

<h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Nano-Çaprazlayıcı Dizinler ile Hesaplama </h2> | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Nano-Çaprazlayıcı Dizinler ile Hesaplama </h2> | ||

| Line 22: | Line 275: | ||

Teknoloji Geliştirme</h3> | Teknoloji Geliştirme</h3> | ||

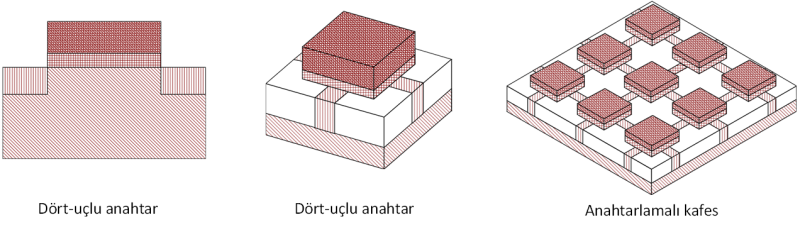

| − | Dört-uçlu anahtar tabanlı bir dizin, iki-uçlu anahtarlara kıyasla, anahtar sayısı bakımından '''önemli bir alan avantajı''' sunsa da, teknoloji seviyesinde gerçekleştirilmesi henüz net olarak cevaplanmamıştır. Bu ihtiyacı karşılamak için | + | Dört-uçlu anahtar tabanlı bir dizin, iki-uçlu anahtarlara kıyasla, anahtar sayısı bakımından '''önemli bir alan avantajı''' sunsa da, teknoloji seviyesinde gerçekleştirilmesi henüz net olarak cevaplanmamıştır. Bu ihtiyacı karşılamak için, üç boyutlu teknoloji bilgisayar destekli tasarım (TCAD) simülasyonları kullanarak, '''dört-uçlu anahtarların doğrudan CMOS teknolojisi ile gerçeklenebileceğini gösterdik'''. Ardından, TCAD simülasyon verilerini standart CMOS akım-gerilim denklemlerine uyarlayarak, dört-uçlu bir anahtarın Spice modelini geliştirdik. |

| − | + | ||

| − | + | ||

<h3> | <h3> | ||

| Line 78: | Line 329: | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PPT.jpg|60px|link= | + | [[File:PPT.jpg|60px|link=https://www.ecc.itu.edu.tr/images/7/71/Safaltin_EtAl_Technology_Development_for_Switching_Lattices.pptx]] |

</span> | </span> | ||

| − | <br> [ | + | <br> [https://www.ecc.itu.edu.tr/images/7/71/Safaltin_EtAl_Technology_Development_for_Switching_Lattices.pptx Sunum] |

|} | |} | ||

| Line 107: | Line 358: | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PPT.jpg|60px|link= | + | [[File:PPT.jpg|60px|link=https://www.ecc.itu.edu.tr/images/b/b8/Tunali_Altun_Logic_Synthesis_and_Defect_Tolerance_for_Memristive_Crossbars.pptx]] |

</span> | </span> | ||

| − | <br> [ | + | <br> [https://www.ecc.itu.edu.tr/images/b/b8/Tunali_Altun_Logic_Synthesis_and_Defect_Tolerance_for_Memristive_Crossbars.pptx Sunum] |

|} | |} | ||

| Line 138: | Line 389: | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PDF.png|65px|link= | + | [[File:PDF.png|65px|link=https://www.ecc.itu.edu.tr/images/7/7f/Altun_EtAl_Synthesis_and_Performance_Optimization_of_a_Switching_Nano-crossbar_Computer_SLIDES.pdf]] |

</span> | </span> | ||

<br> [[Media:Altun_EtAl_Synthesis_and_Performance_Optimization_of_a_Switching_Nano-crossbar_Computer_SLIDES.pdf | Sunum]] | <br> [[Media:Altun_EtAl_Synthesis_and_Performance_Optimization_of_a_Switching_Nano-crossbar_Computer_SLIDES.pdf | Sunum]] | ||

| Line 167: | Line 418: | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PPT.jpg|60px|link= | + | [[File:PPT.jpg|60px|link=https://www.ecc.itu.edu.tr/images/f/f9/Tunali_Altun_Defect_Tolerance_in_Diode_FET_and_Four-Terminal_Switch_based_Nano-Crossbar_Arrays.pptx]] |

</span> | </span> | ||

| − | <br> [ | + | <br> [https://www.ecc.itu.edu.tr/images/f/f9/Tunali_Altun_Defect_Tolerance_in_Diode_FET_and_Four-Terminal_Switch_based_Nano-Crossbar_Arrays.pptx Sunum] |

|} | |} | ||

| Line 198: | Line 449: | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PPT.jpg|60px|link= | + | [[File:PPT.jpg|60px|link=https://www.ecc.itu.edu.tr/images/2/28/Altun_Riedel_Lattice-Based_Computation_of_Boolean_Functions.ppt]] |

</span> | </span> | ||

| − | <br> [ | + | <br> [https://www.ecc.itu.edu.tr/images/2/28/Altun_Riedel_Lattice-Based_Computation_of_Boolean_Functions.ppt Sunum] |

|} | |} | ||

--> | --> | ||

| Line 214: | Line 465: | ||

|- valign=top | |- valign=top | ||

| width="696" |'''Proje Desteği''' | | width="696" |'''Proje Desteği''' | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

|} | |} | ||

| Line 256: | Line 482: | ||

|- valign="top" | |- valign="top" | ||

| '''süre''': | | '''süre''': | ||

| − | | 2015-2019 | + | | 2015-2019, ''tamamlandı'' |

|} | |} | ||

{| style="margin-left: auto; margin-right: 0px; border:0.1px solid #abd5ff; background:#f1f5fc; padding:0.2em 0em;" | {| style="margin-left: auto; margin-right: 0px; border:0.1px solid #abd5ff; background:#f1f5fc; padding:0.2em 0em;" | ||

| Line 295: | Line 521: | ||

|} | |} | ||

| − | + | <!-- STOKASTİK --> | |

| − | <!-- | + | |

{| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | {| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | ||

|- | |- | ||

| − | | colspan="2" style="background:# | + | | colspan="2" style="background:#8FBC8F; text-align:center; padding:1px; border-bottom:1px #8FBC8F solid;" | |

| − | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> | + | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Stokastik Devre Tasarımı </h2> |

|- | |- | ||

| valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | | valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | ||

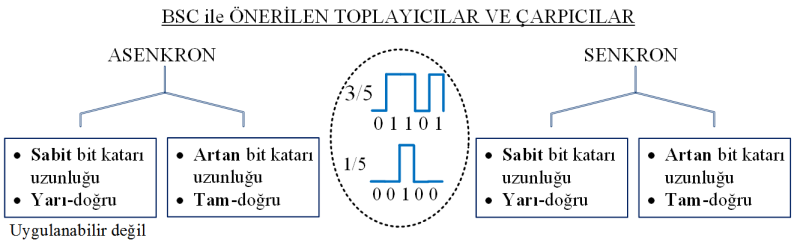

| − | + | Rastgele veya Binom dağılımlı bit katarlarını işleyen yeni bir hesaplama paradigması “'''Bit Stream Computing (BSC)'''” önerdik. Önerilen paradigma, '''stokastik mantığın alan avantajından ve geleneksel ikili mantığın doğruluk avantajından faydalanmaktadır'''. Asenkron veya senkron olarak sınıflandırılmış tam ve yarı doğru aritmetik çarpıcı ve toplayıcı devreler gerçekledik. Bu çalışmanın, geleneksel ikili ve geleneksel stokastik hesaplama tekniklerine alternatif sunarak '''yeni ufuklar''' açtığına inanıyoruz. | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

<!-- <h3> | <!-- <h3> | ||

| + | Yüksek Doğruluklu Aritmetik Gerçeklemeler</h3> | ||

| − | + | Stokastik hesaplamanın en önemli sorunu '''düşük doğruluk''' veya bununla ilişkili olarak '''uzun hesaplama süreleridir'''. Bu soruna, bit katarlarını geri besleme mekanizmalarının da yardımıyla manipüle ederek bir çözüm bulduk. Alan, gecikme ve doğruluk parametrelerini göz önüne alarak hatasız çalışan toplayıcı ve çarpıcı devreler gerçekledik. | |

| − | + | ||

| − | + | ||

--> | --> | ||

| − | + | [[Image:Arastirma_Bit_Stream.png|center|none|800px|link=]] | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

<!-- YAYIN --> | <!-- YAYIN --> | ||

{| id="mp-upper" style="width: 100%; margin:4px 0 0 0; background:none; border-spacing: 0px;" | {| id="mp-upper" style="width: 100%; margin:4px 0 0 0; background:none; border-spacing: 0px;" | ||

| Line 334: | Line 544: | ||

| | | | ||

| − | |||

{| style="border:1px solid #abd5f5; background:#d0e5f5; padding:0.2em 0.5em; font-weight:bold;" | {| style="border:1px solid #abd5f5; background:#d0e5f5; padding:0.2em 0.5em; font-weight:bold;" | ||

| Line 340: | Line 549: | ||

| width="696" |'''Seçilmiş Yayınlar''' | | width="696" |'''Seçilmiş Yayınlar''' | ||

|} | |} | ||

| − | |||

{| style="border:1px solid #abd5f5; background:#f1f5fc;" | {| style="border:1px solid #abd5f5; background:#f1f5fc;" | ||

| | | | ||

| − | {| | + | {| |

|- valign=top | |- valign=top | ||

| width="100" |'''başlık''': | | width="100" |'''başlık''': | ||

| − | | width="450"|[[Media: | + | | width="450"|[[Media:Vahapoglu_Altun_From_Stochastic_To_Bit_Stream_Computing.pdf | From Stochastic to Bit Stream Computing: Accurate Implementation of Arithmetic Circuits and Applications in Neural Networks]] |

|- valign="top" | |- valign="top" | ||

| '''yazarlar''': | | '''yazarlar''': | ||

| − | | | + | | Ensar Vahapoglu ve [[Mustafa Altun]] |

|- valign=top | |- valign=top | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| '''makale''': | | '''makale''': | ||

| − | | | + | | arXiv, 1805.06262, 2018. |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

|- valign=top | |- valign=top | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| '''bildiri''': | | '''bildiri''': | ||

| − | | [http://www. | + | | width="450"| [http://www.eng.ucy.ac.cy/theocharides/isvlsi16/ IEEE Computer Society Annual Symposium on VLSI (ISVLSI)], Pittsburgh, USA, 2016. |

|} | |} | ||

| + | |||

| align=center width="70" | | | align=center width="70" | | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/ | + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/7/73/Vahapoglu_Altun_From_Stochastic_To_Bit_Stream_Computing.pdf]]</span> |

<br> | <br> | ||

| − | [[Media: | + | [[Media:Vahapoglu_Altun_From_Stochastic_To_Bit_Stream_Computing.pdf | Yayın]] |

| align="center" width="70" | | | align="center" width="70" | | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PPT.jpg|60px|link= | + | [[File:PPT.jpg|60px|link=https://www.ecc.itu.edu.tr/images/d/d6/Vahapoglu_Altun_Accurate_Synthesis_of_Arithmetic_Operations_with_Stochastic_Logic.pptx]] |

</span> | </span> | ||

| − | <br> [ | + | <br> [https://www.ecc.itu.edu.tr/images/d/d6/Vahapoglu_Altun_Accurate_Synthesis_of_Arithmetic_Operations_with_Stochastic_Logic.pptx Sunum] |

|} | |} | ||

| − | |||

|} | |} | ||

| Line 427: | Line 587: | ||

| | | | ||

| − | |||

{| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#d0e5f5; padding:0.2em 0.5em; font-weight:bold;" | {| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#d0e5f5; padding:0.2em 0.5em; font-weight:bold;" | ||

| Line 439: | Line 598: | ||

|- valign="top" | |- valign="top" | ||

| width="140" |'''başlık''': | | width="140" |'''başlık''': | ||

| − | | width="558"| | + | | width="558"|Yüksek Doğruluklu Stokastik Devre Bloklarının Gerçeklenmesi ve Yazdırılabilir/Esnek Elektronik Sistemlerde Kullanımı |

|- valign="top" | |- valign="top" | ||

| '''kurum & program''': | | '''kurum & program''': | ||

| − | | [http://www.tubitak.gov.tr/tr/destekler/akademik/ulusal-destek-programlari/icerik- | + | | [http://www.tubitak.gov.tr/tr/destekler/akademik/ulusal-destek-programlari/icerik-1001-bilimsel-ve-teknolojik-arastirma-projelerini-destekleme-pr TÜBİTAK Bilimsel ve Teknolojik Araştırma Projelerini Destekleme Programı (1001)] |

|- valign="top" | |- valign="top" | ||

| '''bütçe''': | | '''bütçe''': | ||

| − | | | + | | 260.000 TL |

|- valign="top" | |- valign="top" | ||

| '''süre''': | | '''süre''': | ||

| − | | | + | | 2017-2020, ''tamamlandı'' |

|} | |} | ||

{| style="margin-left: auto; margin-right: 0px; border:0.1px solid #abd5ff; background:#f1f5fc; padding:0.2em 0em;" | {| style="margin-left: auto; margin-right: 0px; border:0.1px solid #abd5ff; background:#f1f5fc; padding:0.2em 0em;" | ||

|- valign="top" | |- valign="top" | ||

| width="140" |'''proje hedefi''': | | width="140" |'''proje hedefi''': | ||

| − | | width="558"| | + | | width="558"| Stokastik hesaplamada hatayı azaltmak, hatasız aritmetik blokları gerçeklemek ve bu blokları geniş alan elektroniğinde kullanmak. |

|} | |} | ||

|} | |} | ||

| − | <!--{| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#f1f5fc;" | + | |

| + | <!-- {| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#f1f5fc;" | ||

| | | | ||

| Line 463: | Line 623: | ||

|- valign=top | |- valign=top | ||

| width="140" |'''başlık''': | | width="140" |'''başlık''': | ||

| − | | width="558"| | + | | width="558"| Stokastik Mantık ile Yüksek Doğruluklu Aritmetik İşlem Bloklarının Kapı ve Transistor Seviyesinde Gerçeklenmesi |

|- valign="top" | |- valign="top" | ||

| '''kurum & program''': | | '''kurum & program''': | ||

| Line 469: | Line 629: | ||

|- valign="top" | |- valign="top" | ||

| '''süre''': | | '''süre''': | ||

| − | | | + | | 2017-2019, ''tamamlandı'' |

|} | |} | ||

| − | |}--> | + | |} --> |

| − | + | ||

|} | |} | ||

|} | |} | ||

| Line 479: | Line 638: | ||

| − | <!-- | + | <!-- YAKLAŞIK --> |

{| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | {| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | ||

|- | |- | ||

| − | | colspan="2" style="background:# | + | | colspan="2" style="background:#8FBC7F; text-align:center; padding:1px; border-bottom:1px #8FBC7F solid;" | |

| − | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> | + | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Yaklaşık Devre ve Sistem Tasarımı </h2> |

|- | |- | ||

| valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | | valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | ||

| − | + | <!-- | |

<h3> | <h3> | ||

| − | + | Güç Verimli Yaklaşık Sistem Tasarım Metodolojisi</h3> | |

| + | --> | ||

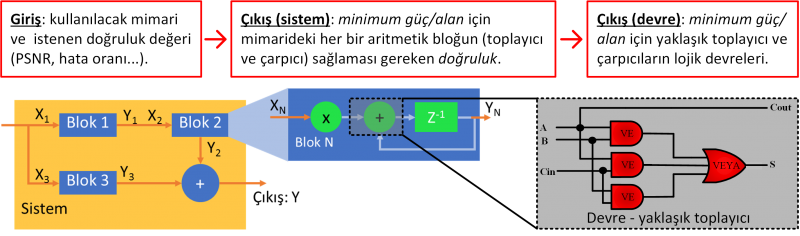

| − | + | Bu çalışma, '''sistem düzeyinde tasarımın istenen doğrulukta olması için devre düzeyinde tasarımın güç/alan verimliliğini sağlar'''. İlk önce devre seviyesinde yaklaşık hesaplama blokları, genellikle toplayıcılar ve çarpıcılar, tasarladık. Daha sonra sistem seviyesinde, toplam hesaplama maliyetini en aza indiren ancak nihai performansı koruyan yaklaşık hesaplama birimlerini seçen bir yöntem geliştirildi. Yöntem, her bloğun yeterli çıktı kalitesini belirlemek için toplam sistemi en üst seviyeden aritmetik birimlerine kadar araştırmaktadır. | |

| − | [[Image: | + | [[Image:Arastirma-yaklasik.png|center|none|800px|link=]] |

<!-- YAYIN --> | <!-- YAYIN --> | ||

| Line 501: | Line 661: | ||

| | | | ||

| + | |||

{| style="border:1px solid #abd5f5; background:#d0e5f5; padding:0.2em 0.5em; font-weight:bold;" | {| style="border:1px solid #abd5f5; background:#d0e5f5; padding:0.2em 0.5em; font-weight:bold;" | ||

| Line 507: | Line 668: | ||

|} | |} | ||

{| style="border:1px solid #abd5f5; background:#f1f5fc;" | {| style="border:1px solid #abd5f5; background:#f1f5fc;" | ||

| + | | | ||

| + | {| | ||

| + | |- valign=top | ||

| + | | width="100" |'''title''': | ||

| + | | width="450"|[[Media:Nojehdeh_Altun_Approximate_Adders_Multipliers.pdf | Systematic Synthesis of Approximate Adders and Multipliers with Accurate Error Calculations]] | ||

| + | |- valign="top" | ||

| + | | '''yazarlar''': | ||

| + | | Mohammadreza Nojehdeh ve [[Mustafa Altun]] | ||

| + | |- valign="top" | ||

| + | | '''makale''': | ||

| + | | width="450" | [http://www.journals.elsevier.com/integration Integration, the VLSI Journal], Vol. 70, pp. 99–107, 2020. | ||

| + | |- valign=top | ||

| + | | '''bildiri''': | ||

| + | | width="450"| [http://www.eng.ucy.ac.cy/theocharides/isvlsi20/ IEEE Computer Society Annual Symposium on VLSI (ISVLSI)], Limassol, Cyprus, 2020. | ||

| + | |} | ||

| + | | align=center width="70" | | ||

| + | <span class="plainlinks"> | ||

| + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/c/c8/Nojehdeh_Altun_Approximate_Adders_Multipliers.pdf]]</span> | ||

| + | <br> | ||

| + | [[Media:Nojehdeh_Altun_Approximate_Adders_Multipliers.pdf | Yayın]] | ||

| + | | align="center" width="70" | | ||

| + | <span class="plainlinks"> | ||

| + | [[File:PPT.jpg|60px|link=https://www.ecc.itu.edu.tr/images/7/7f/Nojehdeh_Aksoy_Altun_Approximate_ANN.pptx]] | ||

| + | </span> | ||

| + | <br> [https://www.ecc.itu.edu.tr/images/7/7f/Nojehdeh_Aksoy_Altun_Approximate_ANN.pptx Sunum] | ||

| + | |} | ||

| + | {| style="border:1px solid #abd5f5; background:#f1f5fc;" | ||

| | | | ||

| − | {| | + | {| |

|- valign=top | |- valign=top | ||

| width="100" |'''başlık''': | | width="100" |'''başlık''': | ||

| − | | width="450"|[[Media: | + | | width="450"|[[Media:Ayhan_Altun_Circuit_Aware_Approximate_System_Design.pdf| Circuit Aware Approximate System Design with Case Studies in Image Processing and Neural Networks]] |

|- valign="top" | |- valign="top" | ||

| '''yazarlar''': | | '''yazarlar''': | ||

| − | | | + | | Tuba Ayhan ve [[Mustafa Altun]] |

| + | |- valign="top" | ||

| + | | '''makale''': | ||

| + | | [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6287639 IEEE Access], Vol. 7, pp. 4726–4734, 2019. | ||

|- valign=top | |- valign=top | ||

| '''bildiri''': | | '''bildiri''': | ||

| − | | [http://www. | + | | width="450"| [http://www.eng.ucy.ac.cy/theocharides/isvlsi17/ IEEE Computer Society Annual Symposium on VLSI (ISVLSI)], Bochum, Germany, 2017. |

|} | |} | ||

| − | | align=center width="70" | | + | | align=center width="70" | |

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/ | + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/9/90/Ayhan_Altun_Circuit_Aware_Approximate_System_Design.pdf]]</span> |

<br> | <br> | ||

| − | [[Media: | + | [[Media:Ayhan_Altun_Circuit_Aware_Approximate_System_Design.pdf | Yayın]] |

| − | | align="center" width="70" | | + | | align="center" width="70" | |

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PPT.jpg|60px|link= | + | [[File:PPT.jpg|60px|link=https://www.ecc.itu.edu.tr/images/8/86/Ayhan_Kula_Altun_Approximate_System_Design_Methodology.pptx]] |

</span> | </span> | ||

| − | <br> [ | + | <br> [https://www.ecc.itu.edu.tr/images/8/86/Ayhan_Kula_Altun_Approximate_System_Design_Methodology.pptx Sunum] |

|} | |} | ||

| + | |||

|} | |} | ||

| Line 541: | Line 733: | ||

| | | | ||

| + | |||

{| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#d0e5f5; padding:0.2em 0.5em; font-weight:bold;" | {| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#d0e5f5; padding:0.2em 0.5em; font-weight:bold;" | ||

| Line 546: | Line 739: | ||

| width="696" |'''Proje Desteği''' | | width="696" |'''Proje Desteği''' | ||

|} | |} | ||

| + | |||

{| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#f1f5fc;" | {| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#f1f5fc;" | ||

| Line 552: | Line 746: | ||

|- valign="top" | |- valign="top" | ||

| width="140" |'''başlık''': | | width="140" |'''başlık''': | ||

| − | | width="558"| | + | | width="558"|Yaklaşık Hesaplama Yapabilen Yeniden Yapılandırılabilir Devre ve Sistemlerin Tasarımı ve Öğrenme İçeren Görüntü İşleme Uygulamalarında Kullanılması |

|- valign="top" | |- valign="top" | ||

| '''kurum & program''': | | '''kurum & program''': | ||

| Line 558: | Line 752: | ||

|- valign="top" | |- valign="top" | ||

| '''bütçe''': | | '''bütçe''': | ||

| − | | | + | | 230.000 TL |

|- valign="top" | |- valign="top" | ||

| '''süre''': | | '''süre''': | ||

| − | | | + | | 2018-2020, ''tamamlandı'' |

|} | |} | ||

{| style="margin-left: auto; margin-right: 0px; border:0.1px solid #abd5ff; background:#f1f5fc; padding:0.2em 0em;" | {| style="margin-left: auto; margin-right: 0px; border:0.1px solid #abd5ff; background:#f1f5fc; padding:0.2em 0em;" | ||

|- valign="top" | |- valign="top" | ||

| width="140" |'''proje hedefi''': | | width="140" |'''proje hedefi''': | ||

| − | | width="558"| | + | | width="558"| Sistemden istenen doğruluk veya kalite seviyesine bağlı olarak her devre bloğunun gerekli doğruluk performansını belirleyerek minimum güç/enerji tüketimi için en uygun çözümleri hiyerarşik bir yaklaşımla bulmak. |

| − | + | ||

| − | + | ||

|} | |} | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

|} | |} | ||

| − | |||

| − | |||

| − | |||

|} | |} | ||

|} | |} | ||

|} | |} | ||

| − | + | <!-- QUANTUM --> | |

| − | <!-- | + | |

{| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | {| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | ||

|- | |- | ||

| − | | colspan="2" style="background:# | + | | colspan="2" style="background:#8FBC6F; text-align:center; padding:1px; border-bottom:1px #8FBC6F solid;" | |

| − | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> | + | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Tersinir Hesaplama</h2> |

|- | |- | ||

| valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | | valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | ||

| + | |||

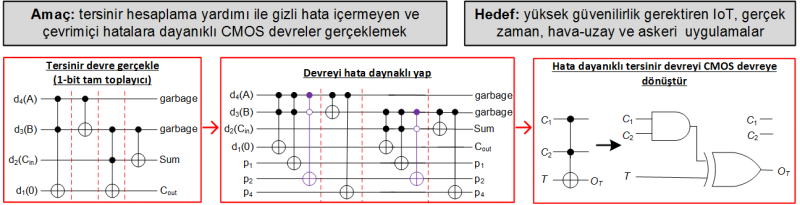

| + | Geleneksel CMOS devrelerinden farklı olarak, tersinir devreler gizli hatalara sahip değildir, bu nedenle dahili devre düğümlerinde meydana gelen hatalar her zaman çıkışta bir hataya neden olur. Bu, çevrimiçi veya eşzamanlı hata toleransı için eşsiz bir özelliktir. Bu durumdan hareketle, tersinir hesaplamayı kullanarak hataya dayanıklı CMOS devre blokları gerçekliyoruz. Öncelikle tersinir kapılarla tersinir devreler sentezliyoruz; sonra onları hataya dayanıklı hale getiriyoruz; ve son olarak tersinir kapılardan CMOS kapılara dönüşümü yapıyoruz. | ||

| + | |||

| + | [[Image:Research-reversible_tr-3.png|center|none|800px|link=]] | ||

<h3> | <h3> | ||

| − | |||

| + | Mükemmel Hata Tespiti</h3> | ||

| − | + | Tersinir hesaplamadan yararlanarak % '''100 çevrimiçi veya eşzamanlı hata tespitine sahip CMOS devreleri''' sentezledik. Bu amaç için tersinir parite korunumlu bir kapı kütüphanesi önerdik. | |

| + | <!-- <h3> | ||

| − | + | Sentez</h3> | |

| + | Tersinir Boolean fonksiyonları kuantum kapılar ile gerçekleyen hızlı bir algoritma önerdik. Önerdiğimiz algoritma, her bir fonksiyon için zaman alıcı bir arama yapmak yerine '''temel fonksiyonları''' kullanmaktadır ve sonrasında '''sıralama''' yapmaktadır. Örnek vermek gerekirse, toplamda 20922789888000 fonksiyonun olduğu 4 bit devrelerdeki temel fonksiyon sayısı yalnızca 120'dir. Buna ek olarak, komşu kapı çiftlerini göz önüne alarak '''tersinir ve kuantum devre masraflarını''' optimize ettik. | ||

| + | --> | ||

| + | <h3> | ||

| + | |||

| + | Çevrimiçi Hata Tespiti ve Düzeltme </h3> | ||

| + | |||

| + | Çoklu kontrol Toffoli kapılarını kullanarak tersine çevrilebilir bir devrede hataya dayanıklı hale getirmek için iki teknik geliştiriyoruz. İlk | ||

| + | olarak, '''tek parite korumasına dayanan''' ve çıktıdaki tek sayıdaki hataları tespit edebilen bir teknik geliştirdik. İkinci teknik ise '''Hamming kodları''' üzerine inşa edilen bir hata düzeltme tekniğidir. Aynı zamanda, Fredkin kapısı gibi korunumlu tersinir kapılarla mükemmel hata tespitinin mümkün olduğunu gösterdik. Bir sonraki adım olarak, önerilen '''tersinir devreleri geleneksel CMOS kapılarından oluşan devrelere''' dönüştürdük. | ||

| + | |||

| + | <!-- [[Image:Arastirma-4.png|center|none|800px|link=]] --> | ||

<!-- YAYIN --> | <!-- YAYIN --> | ||

{| id="mp-upper" style="width: 100%; margin:4px 0 0 0; background:none; border-spacing: 0px;" | {| id="mp-upper" style="width: 100%; margin:4px 0 0 0; background:none; border-spacing: 0px;" | ||

| Line 622: | Line 811: | ||

| width="696" |'''Seçilmiş Yayınlar''' | | width="696" |'''Seçilmiş Yayınlar''' | ||

|} | |} | ||

| + | |||

{| style="border:1px solid #abd5f5; background:#f1f5fc;" | {| style="border:1px solid #abd5f5; background:#f1f5fc;" | ||

| + | |||

| | | | ||

{| | {| | ||

|- valign=top | |- valign=top | ||

| width="100" |'''başlık''': | | width="100" |'''başlık''': | ||

| − | | width="450"|[[Media: | + | | width="450"|[[Media:Parvin_Altun_Perfect_Concurrent_Fault_Detection.pdf| Perfect Concurrent Fault Detection in CMOS Logic Circuits Using Parity Preservative Reversible Gates]] |

|- valign="top" | |- valign="top" | ||

| '''yazarlar''': | | '''yazarlar''': | ||

| − | | | + | | Sajjad Parvin ve [[Mustafa Altun]] |

|- valign="top" | |- valign="top" | ||

| '''makale''': | | '''makale''': | ||

| − | | [http:// | + | | [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6287639 IEEE Access], Vol. 7, pp. 163939–163947, 2019. |

|- valign=top | |- valign=top | ||

| '''bildiri''': | | '''bildiri''': | ||

| − | | width="450"| [http:// | + | | width="450"| [http://tima.univ-grenoble-alpes.fr/conferences/iolts/iolts19/ IEEE International Symposium on On-Line Testing and Robust System Design (IOLTS)], Rhodes Island, Greece, 2019. |

|} | |} | ||

| align=center width="70" | | | align=center width="70" | | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/ | + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/3/3c/Parvin_Altun_Perfect_Concurrent_Fault_Detection.pdf]]</span> |

<br> | <br> | ||

| − | [[Media: | + | [[Media:Parvin_Altun_Perfect_Concurrent_Fault_Detection.pdf | Yayın]] |

| align="center" width="70" | | | align="center" width="70" | | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PPT.jpg|60px|link= | + | [[File:PPT.jpg|60px|link=https://www.ecc.itu.edu.tr/images/f/f4/Parvin_Altun_CMOS_Fault_Tolerance_with_Preservative_Reversible_Gates.pptx]] |

</span> | </span> | ||

| − | <br> [ | + | <br> [https://www.ecc.itu.edu.tr/images/f/f4/Parvin_Altun_CMOS_Fault_Tolerance_with_Preservative_Reversible_Gates.pptx Sunum] |

|} | |} | ||

| + | {| style="border:1px solid #abd5f5; background:#f1f5fc;" | ||

| + | | | ||

| + | {| | ||

| + | |- valign=top | ||

| + | | width="100" |'''başlık''': | ||

| + | | width="524"|[[Media:Altun_Parvin_Cilasun_Exploiting_Reversible_Computing_for_CMOS_Fault_Tolerance.pdf| Exploiting Reversible Computing for Latent-Fault-Free Error Detecting/Correcting CMOS Circuits | ||

| + | ]] | ||

| + | |- valign="top" | ||

| + | | '''yazarlar''': | ||

| + | | [[Mustafa Altun]], Sajjad Parvin, and Husrev Cilasun | ||

| + | |- valign="top" | ||

| + | | '''makale''': | ||

| + | | width="524" | [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6287639 IEEE Access], Vol. 6, pp. 74475–74484, 2018. | ||

| + | |} | ||

| + | | align=center width="70" | | ||

| + | <span class="plainlinks"> | ||

| + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/7/7d/Altun_Parvin_Cilasun_Exploiting_Reversible_Computing_for_CMOS_Fault_Tolerance.pdf]]</span> | ||

| + | <br> | ||

| + | [[Media:Altun_Parvin_Cilasun_Exploiting_Reversible_Computing_for_CMOS_Fault_Tolerance.pdf | Yayın]] | ||

| + | |} | ||

| + | <!-- {| style="border:1px solid #abd5f5; background:#f1f5fc;" | ||

| + | |||

| + | | | ||

| + | {| | ||

| + | |- valign=top | ||

| + | | width="100" |'''başlık''': | ||

| + | | width="450"|[[Media:Susam_Altun_Fast_Synthesis_of_Reversible_Circuits_using_a_Sorting_Algorithm_and_Optimization.pdf| Fast Synthesis of Reversible Circuits using a Sorting Algorithm and Optimization]] | ||

| + | |- valign="top" | ||

| + | | '''yazarlar''': | ||

| + | | Ömercan Susam ve [[Mustafa Altun]] | ||

| + | |- valign="top" | ||

| + | | '''makale''': | ||

| + | | width="450"| [http://www.oldcitypublishing.com/journals/mvlsc-home/ Journal of Multiple-Valued Logic and Soft Computing], Vol. 29, Issue 1-2, pp. 1–23, 2017. | ||

| + | |- valign="top" | ||

| + | | '''bildiri''': | ||

| + | | [http://www.ieee-icecs2014.org/ IEEE International Conference on Electronics Circuits and Systems<br> (ICECS)], Marseille, France, 2014. | ||

| + | |} | ||

| + | | align=center width="70" | | ||

| + | <span class="plainlinks"> | ||

| + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/c/cd/Susam_Altun_Fast_Synthesis_of_Reversible_Circuits_using_a_Sorting_Algorithm_and_Optimization.pdf]]</span> | ||

| + | <br> | ||

| + | [[Media:Susam_Altun_Fast_Synthesis_of_Reversible_Circuits_using_a_Sorting_Algorithm_and_Optimization.pdf | Yayın]] | ||

| + | | align="center" width="70" | | ||

| + | <span class="plainlinks"> | ||

| + | |||

| + | [[File:PPT.jpg|60px|link=https://www.ecc.itu.edu.tr/images/d/d0/Susam_Altun_An_Efficient_Algorithm_to_Synthesize_Quantum_Circuits_and_Optimization.pptx]] | ||

| + | </span> | ||

| + | <br> [https://www.ecc.itu.edu.tr/images/d/d0/Susam_Altun_An_Efficient_Algorithm_to_Synthesize_Quantum_Circuits_and_Optimization.pptx Sunum] | ||

| + | |} | ||

| + | --> | ||

|} | |} | ||

| Line 666: | Line 907: | ||

| width="696" |'''Proje Desteği''' | | width="696" |'''Proje Desteği''' | ||

|} | |} | ||

| − | |||

{| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#f1f5fc;" | {| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#f1f5fc;" | ||

| Line 673: | Line 913: | ||

|- valign="top" | |- valign="top" | ||

| width="140" |'''başlık''': | | width="140" |'''başlık''': | ||

| − | | width="558"| | + | | width="558"| Hata Farkındalıklı 8-bitlik bir Tersinir Mikroişlemci Gerçeklemesi |

|- valign="top" | |- valign="top" | ||

| '''kurum & program''': | | '''kurum & program''': | ||

| − | | [http://www.tubitak.gov.tr/tr/destekler/akademik/ulusal-destek-programlari/icerik- | + | | [http://www.tubitak.gov.tr/tr/destekler/akademik/ulusal-destek-programlari/icerik-1002-hizli-destek-programi TÜBİTAK Hızlı Destek Programı (1002)] |

|- valign="top" | |- valign="top" | ||

| '''bütçe''': | | '''bütçe''': | ||

| − | | | + | | 30.000 TL |

|- valign="top" | |- valign="top" | ||

| '''süre''': | | '''süre''': | ||

| − | | | + | | 2016-2017, ''tamamlandı'' |

|} | |} | ||

{| style="margin-left: auto; margin-right: 0px; border:0.1px solid #abd5ff; background:#f1f5fc; padding:0.2em 0em;" | {| style="margin-left: auto; margin-right: 0px; border:0.1px solid #abd5ff; background:#f1f5fc; padding:0.2em 0em;" | ||

|- valign="top" | |- valign="top" | ||

| width="140" |'''proje hedefi''': | | width="140" |'''proje hedefi''': | ||

| − | | width="558"| | + | | width="558"| Çevrimiçi hataları tespit edebilen tersinir devreleri ve bunların CMOS devre karşılıklarını gerçeklemek. |

| + | |||

| + | |} | ||

|} | |} | ||

| + | <!--{| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#f1f5fc;" | ||

| + | |||

| + | | | ||

| + | {| | ||

| + | |- valign=top | ||

| + | | width="140" |'''başlık''': | ||

| + | | width="558"|Kuantum Devre Tasarımı ve Hesaplama | ||

| + | |- valign="top" | ||

| + | | '''kurum & program''': | ||

| + | | [http://bap.itu.edu.tr/ İstanbul Teknik Üniversitesi Bilimsel Araştırmalar Programı (İTÜ-BAP)] | ||

| + | |- valign="top" | ||

| + | | '''süre''': | ||

| + | | 2014-2015, ''tamamlandı'' | ||

|} | |} | ||

| + | |||

| + | |}--> | ||

| + | |||

|} | |} | ||

|} | |} | ||

| Line 698: | Line 956: | ||

{| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | {| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | ||

|- | |- | ||

| − | | colspan="2" style="background:# | + | | colspan="2" style="background:#8FBC5F; text-align:center; padding:1px; border-bottom:1px #8FBC5F solid;" | |

<h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Elektronik Ürünlerin Güvenilirliği </h2> | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Elektronik Ürünlerin Güvenilirliği </h2> | ||

|- | |- | ||

| Line 717: | Line 975: | ||

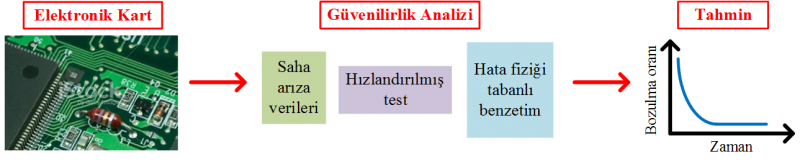

ZnO varistörlerde görülen değişik bozunum mekanizmalarını inceledik. Varistör voltajı Vv'nin değişik stres seviyelerinde nasıl değiştiğini modelledik. Bu amaç için, değişik AC akımlar kullanarak hızlandırılmış testler uyguladık ve Vv değerlerini ölçtük. Literatürdeki genel kanının aksine sadece '''düşen Vv değerleri''' değil, '''yükselen Vv değerleri''' de gözlemledik. | ZnO varistörlerde görülen değişik bozunum mekanizmalarını inceledik. Varistör voltajı Vv'nin değişik stres seviyelerinde nasıl değiştiğini modelledik. Bu amaç için, değişik AC akımlar kullanarak hızlandırılmış testler uyguladık ve Vv değerlerini ölçtük. Literatürdeki genel kanının aksine sadece '''düşen Vv değerleri''' değil, '''yükselen Vv değerleri''' de gözlemledik. | ||

| − | + | <!-- | |

<h3> | <h3> | ||

Kalibreli Hızlandırılmış Testler</h3> | Kalibreli Hızlandırılmış Testler</h3> | ||

Elektronik ürünlerin hata oranlarındaki önemli azalma, geleneksel '''ALT''' (accelerated life tests) kullanımını oldukça masraflı ve zaman alıcı bir hale getirmiştir. Bu aşamada yeni bir test metodolojisi olan '''CALT''' (calibrated accelerated life tests) önerilmiştir. Bu çalışmada, ALT ve CALT testlerini detaylı olarak karşılaştırdık; hata oranı, hızlandırma faktörü ve stres seviyesinin test süresine olan etkilerini inceledik. | Elektronik ürünlerin hata oranlarındaki önemli azalma, geleneksel '''ALT''' (accelerated life tests) kullanımını oldukça masraflı ve zaman alıcı bir hale getirmiştir. Bu aşamada yeni bir test metodolojisi olan '''CALT''' (calibrated accelerated life tests) önerilmiştir. Bu çalışmada, ALT ve CALT testlerini detaylı olarak karşılaştırdık; hata oranı, hızlandırma faktörü ve stres seviyesinin test süresine olan etkilerini inceledik. | ||

| − | + | --> | |

<!-- YAYIN --> | <!-- YAYIN --> | ||

{| id="mp-upper" style="width: 100%; margin:4px 0 0 0; background:none; border-spacing: 0px;" | {| id="mp-upper" style="width: 100%; margin:4px 0 0 0; background:none; border-spacing: 0px;" | ||

| Line 762: | Line 1,020: | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PPT.jpg|60px|link= | + | [[File:PPT.jpg|60px|link=https://www.ecc.itu.edu.tr/images/a/a7/Comert_Altun_Nadar_Erturk_Warranty_Forecasting_of_Electronic_Boards_using_Short-term_Field_Data.pptx]] |

</span> | </span> | ||

| − | <br> [ | + | <br> [https://www.ecc.itu.edu.tr/images/a/a7/Comert_Altun_Nadar_Erturk_Warranty_Forecasting_of_Electronic_Boards_using_Short-term_Field_Data.pptx Sunum] |

|} | |} | ||

| Line 792: | Line 1,050: | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PPT.jpg|60px|link= | + | [[File:PPT.jpg|60px|link=https://www.ecc.itu.edu.tr/images/d/de/Yadavari_EtAl_Effects_of_ZnO_Varistor_Degradation_on_the_Overvoltage_Protection_Mechanism_of_Electronic_Boards.pptx]] |

</span> | </span> | ||

| − | <br> [ | + | <br> [https://www.ecc.itu.edu.tr/images/d/de/Yadavari_EtAl_Effects_of_ZnO_Varistor_Degradation_on_the_Overvoltage_Protection_Mechanism_of_Electronic_Boards.pptx Sunum] |

|} | |} | ||

| − | {| style="border:1px solid #abd5f5; background:#f1f5fc;" | + | <!-- {| style="border:1px solid #abd5f5; background:#f1f5fc;" |

| | | | ||

| Line 819: | Line 1,077: | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PPT.jpg|60px|link= | + | [[File:PPT.jpg|60px|link=https://www.ecc.itu.edu.tr/images/a/a8/Sal_Altun_Extensive_Investigation_of_CALT_in_Comparison_with_ALT.pptx]] |

</span> | </span> | ||

| − | <br> [ | + | <br> [https://www.ecc.itu.edu.tr/images/a/a8/Sal_Altun_Extensive_Investigation_of_CALT_in_Comparison_with_ALT.pptx Sunum] |

| − | |} | + | |} --> |

| − | |} | + | |} |

| style="border:1px solid transparent;" | | | style="border:1px solid transparent;" | | ||

<!-- PROJE --> | <!-- PROJE --> | ||

| Line 858: | Line 1,116: | ||

|} | |} | ||

|} | |} | ||

| − | {| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#f1f5fc;" | + | <!-- {| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#f1f5fc;" |

| | | | ||

| Line 873: | Line 1,131: | ||

|} | |} | ||

| − | |} | + | |} --> |

|} | |} | ||

| Line 884: | Line 1,142: | ||

{| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | {| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | ||

|- | |- | ||

| − | | colspan="2" style="background:# | + | | colspan="2" style="background:#8FBC4F; text-align:center; padding:1px; border-bottom:1px #8FBC4F solid;" | |

<h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Analog Devre Tasarımı </h2> | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Analog Devre Tasarımı </h2> | ||

|- | |- | ||

| Line 930: | Line 1,188: | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PPT.jpg|60px|link= | + | [[File:PPT.jpg|60px|link=https://www.ecc.itu.edu.tr/images/7/77/Altun_Kuntman_A_Wideband_CMOS_Current-Mode_Operational_Amplifier_and_Its_Use_for_Band-Pass_Filter_Realization.ppt]] |

</span> | </span> | ||

| − | <br> [ | + | <br> [https://www.ecc.itu.edu.tr/images/7/77/Altun_Kuntman_A_Wideband_CMOS_Current-Mode_Operational_Amplifier_and_Its_Use_for_Band-Pass_Filter_Realization.ppt Sunum] |

|} | |} | ||

| Line 947: | Line 1,205: | ||

{| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | {| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | ||

|- | |- | ||

| − | | colspan="2" style="background:# | + | | colspan="2" style="background:#8FBC3F; text-align:center; padding:1px; border-bottom:1px #8FBC3F solid;" | |

<h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Ayrık Matematik </h2> | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Ayrık Matematik </h2> | ||

|- | |- | ||

| Line 990: | Line 1,248: | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PPT.jpg|60px|link= | + | [[File:PPT.jpg|60px|link=https://www.ecc.itu.edu.tr/images/1/18/Altun_Riedel_A_Study_on_Monotone_Self_Dual_Boolean_Functions.ppt]] |

</span> | </span> | ||

| − | <br> [ | + | <br> [https://www.ecc.itu.edu.tr/images/1/18/Altun_Riedel_A_Study_on_Monotone_Self_Dual_Boolean_Functions.ppt Sunum] |

|} | |} | ||

Latest revision as of 22:20, 17 April 2023

Araştırmalarımızın amacı, elektronik devre ve sistemler için hesaplama, devre tasarımı ve güvenilirlik konularında yeni yaklaşımlar geliştirmektir. Araştırmalarımız temelde yeni ve gelişen teknolojileri ve hesaplama düzenlerini hedef almaktadır. Aşağıda en yeniden en eskiye ve önem sırasına göre sıralanan araştırma konuları yer almaktadır. Her konu kısaca anlatılmış ve ilgili yayın ve projeler eklenmiştir.

Contents |

Anahtarlamalı Kafesler ile Hesaplama | ||||||||||||||||||||||||||||||||||||||||

|

Dört uçlu anahtarlardan oluşan iki boyutlu bir ağ olarak oluşturulan anahtarlamalı kafes, lojik hesaplama için düzenli, yoğun, alan verimli ve CMOS uyumlu bir yapı olarak sunulmuştur. Kafesin her bir bölümü dört uçlı bir anahtardır ve bir kontrol girişine ve dört terminale sahiptir. Kontrol girişi, tüm terminallerinin bağlantılarını keser (KAPALI) veya tümünün bağlı (AÇIK) olmasını sağlar.  Teknoloji GeliştirmeAnahtarlamalı kafeslerinin CMOS uyumlu olduğunu gösterdik. Bu amaçla, farklı dört uçlu anahtar yapıları önerdik; bunları üç boyutlu teknoloji bilgisayar destekli tasarım (TCAD) ortamında, TSMC 65nm CMOS prosesinin tasarım kurallarını karşılayarak, ve ayrıca Cadence ortamında kurduk ve simülasyonlarını tamamladık. Deneysel sonuçlar, anahtarlamalı kafesleri kullanılarak lojik fonksiyonları gerçeklemenin, geleneksel CMOS gerçeklemeleri ile karşılaştırıldığında çok daha az serim alanı kapladığını ve rekabetçi gecikme ve güç tüketimi değerlerine sahip olduğunu göstermektedir.  Performans OptimizasyonuGecikme kısıtlaması altında kafes boyutlarını optimize etmek için bir lojik sentez algoritması önerdik. Ayrıca kafeslerin alan-gecikme-güç verimliliği için statik ve dinamik lojik çözümleri önerdik. SentezMinimum boyutta anahtarlama kafesler ile lojik fonksiyonları gerçeklemek için optimum ve sezgisel algoritmalar önerdik.

| ||||||||||||||||||||||||||||||||||||||||

Enerji Verimli YSA Donanım gerçeklemesi | |||||||||||||||||||||||||||

|

İleri beslemeli yapay sinir ağlarının (YSA) enerji tüketimini azaltmak için donanıma odaklı eğitim tekniklerini, yeni hibrit bit paralel seri sayı temsillerini ve sabit çarpma tabanlı paylaşım tekniklerini kullanmayı amaçlıyoruz.

| |||||||||||||||||||||||||||

Nano-Çaprazlayıcı Dizinler ile Hesaplama | |||||||||||||||||||||||||||

|

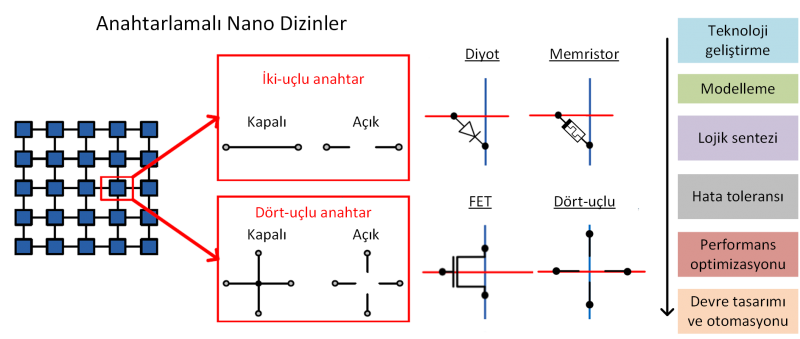

Nano-çaprazlayıcı dizinler yakın gelecekte CMOS'un yerini alacak güçlü bir aday teknoloji olarak ortaya çıkmıştır. Düzenli ve sık yapıdadırlar. Dizinler ile hesaplama, iki-uçlu ya da dört-uçlu anahtarlar gibi davranan çaprazlama noktaları ile elde edilir. Kullanılan teknolojiye bağlı olarak, iki-uçlu bir anahtar, diyot, direnç/memristor veya FET gibi davranır. Öte yandan, dört-uçlu anahtarın tek bir davranışı vardır. İki-uçlu anahtar tabanlı dizinler için önerilen birçok farklı teknoloji olmasına rağmen, dört-uçlu anahtar tabanlı dizinler, anahtarlamalı kafesler, için teknoloji geliştirme yakın zamanda başlamıştır. Hem iki-uçlu hem de dört-uçlu anahtar tabanlı dizinler için, ortaya çıkacak bir nano bilgisayarın tasarımı ve yapımı için tam bir sentez ve performans optimizasyon metodolojisi geliştirmeyi hedefliyoruz. Ayrıca, özellikle anahtarlamalı kafesleri gerçeklemek için CMOS uyumlu teknolojiler geliştirmeyi hedefliyoruz.  Teknoloji GeliştirmeDört-uçlu anahtar tabanlı bir dizin, iki-uçlu anahtarlara kıyasla, anahtar sayısı bakımından önemli bir alan avantajı sunsa da, teknoloji seviyesinde gerçekleştirilmesi henüz net olarak cevaplanmamıştır. Bu ihtiyacı karşılamak için, üç boyutlu teknoloji bilgisayar destekli tasarım (TCAD) simülasyonları kullanarak, dört-uçlu anahtarların doğrudan CMOS teknolojisi ile gerçeklenebileceğini gösterdik. Ardından, TCAD simülasyon verilerini standart CMOS akım-gerilim denklemlerine uyarlayarak, dört-uçlu bir anahtarın Spice modelini geliştirdik. Performans OptimizasyonuMemristor tabanlı dizinleri de içeren nano anahtarlamalı dizinlerin optimizasyonu üzerine çalışıyoruz. Dizilerin alan, gecikme ve güç maliyetlerini dikkate alarak hataya dayanıklı lojik sentez algoritmaları önerdik. Hata ToleransıYeniden ayarlanabilir nano dizinlerde oluşan açık ve kapalı hataları inceledik. Kalıcı hatalar için, sıralama, geri-izleme ve satır eşleştirme tekniklerini kullanan hızlı bir buluşsal algoritma geliştirdik. Yumuşak/geçici hatalar için, tolere edilebilir bütün hata yerlerini yinelemeli bir teknik kullanarak belirledik. SentezBoolean fonksiyonları diyot, FET ve dört-uçlu anahtar tabanlı nano dizinler ile gerçekledik ve dizin boyut formülleri elde ettik. Buna ek olarak, dört-uçlu anahtarlardan oluşan dizinleri optimum sentezleyen bir algoritma geliştirdik.

| |||||||||||||||||||||||||||

Stokastik Devre Tasarımı | |||||||||||||||||||||||||||||

|

Rastgele veya Binom dağılımlı bit katarlarını işleyen yeni bir hesaplama paradigması “Bit Stream Computing (BSC)” önerdik. Önerilen paradigma, stokastik mantığın alan avantajından ve geleneksel ikili mantığın doğruluk avantajından faydalanmaktadır. Asenkron veya senkron olarak sınıflandırılmış tam ve yarı doğru aritmetik çarpıcı ve toplayıcı devreler gerçekledik. Bu çalışmanın, geleneksel ikili ve geleneksel stokastik hesaplama tekniklerine alternatif sunarak yeni ufuklar açtığına inanıyoruz.

| |||||||||||||||||||||||||||||

Yaklaşık Devre ve Sistem Tasarımı | ||||||||||||||||||||||||||||||||||||||||

|

Bu çalışma, sistem düzeyinde tasarımın istenen doğrulukta olması için devre düzeyinde tasarımın güç/alan verimliliğini sağlar. İlk önce devre seviyesinde yaklaşık hesaplama blokları, genellikle toplayıcılar ve çarpıcılar, tasarladık. Daha sonra sistem seviyesinde, toplam hesaplama maliyetini en aza indiren ancak nihai performansı koruyan yaklaşık hesaplama birimlerini seçen bir yöntem geliştirildi. Yöntem, her bloğun yeterli çıktı kalitesini belirlemek için toplam sistemi en üst seviyeden aritmetik birimlerine kadar araştırmaktadır.

| ||||||||||||||||||||||||||||||||||||||||

Tersinir Hesaplama | |||||||||||||||||||||||||||||||||||||

|

Geleneksel CMOS devrelerinden farklı olarak, tersinir devreler gizli hatalara sahip değildir, bu nedenle dahili devre düğümlerinde meydana gelen hatalar her zaman çıkışta bir hataya neden olur. Bu, çevrimiçi veya eşzamanlı hata toleransı için eşsiz bir özelliktir. Bu durumdan hareketle, tersinir hesaplamayı kullanarak hataya dayanıklı CMOS devre blokları gerçekliyoruz. Öncelikle tersinir kapılarla tersinir devreler sentezliyoruz; sonra onları hataya dayanıklı hale getiriyoruz; ve son olarak tersinir kapılardan CMOS kapılara dönüşümü yapıyoruz.  Mükemmel Hata TespitiTersinir hesaplamadan yararlanarak % 100 çevrimiçi veya eşzamanlı hata tespitine sahip CMOS devreleri sentezledik. Bu amaç için tersinir parite korunumlu bir kapı kütüphanesi önerdik. Çevrimiçi Hata Tespiti ve DüzeltmeÇoklu kontrol Toffoli kapılarını kullanarak tersine çevrilebilir bir devrede hataya dayanıklı hale getirmek için iki teknik geliştiriyoruz. İlk olarak, tek parite korumasına dayanan ve çıktıdaki tek sayıdaki hataları tespit edebilen bir teknik geliştirdik. İkinci teknik ise Hamming kodları üzerine inşa edilen bir hata düzeltme tekniğidir. Aynı zamanda, Fredkin kapısı gibi korunumlu tersinir kapılarla mükemmel hata tespitinin mümkün olduğunu gösterdik. Bir sonraki adım olarak, önerilen tersinir devreleri geleneksel CMOS kapılarından oluşan devrelere dönüştürdük.

| |||||||||||||||||||||||||||||||||||||

Elektronik Ürünlerin Güvenilirliği | ||||||||||||||||||||||||||||||||||||||||

|

Elektronik sektöründe yaşanan baş döndürücü gelişmeler, elektronik devre ve sistemlerin güvenilirliği kavramını yeniden şekillendirmiştir. Elektronik ürünlerin günümüzdeki hızlı üretim döngüleri, uzun süreli ve masraflı olan geleneksel hızlandırılmış testlerin öneminin azalmasına neden olmuştur. Biz bu çalışmada görece masrafsız ve yüksek doğruluklu bir güvenilirlik analizi metodolojisi önerdik. Bu noktada saha verileri, yeni hızlandırılmış testler ve hata fiziği tabanlı benzetimlerden yararlandık. Çalışmalarımız Avrupa'nın en büyük ev aletleri ve beyaz eşya üreticilerinden biri olan Arçelik A.Ş. ile birlikte yürütülmüştür.  Saha Verileri ile Güvenilirlik Analizi ve TahminiYüksek miktarda üretilen elektronik ürünler için saha arıza verileri ile güvenilirlik tahmin modeli geliştirdik. Modelimizi, önerdiğimiz değişim noktası tespit metodunu kullanarak Weibul-eksponansiyel dağılımı üzerine inşa ettik. Modelimiz, elektronik kartların kısa süreli saha verilerini kullanarak, garanti süresi içerisindeki güvenilirlik performanslarını yüksek doğrulukta tahmin etmektedir. Bu çalışmada kullandığımız kartların garanti süresi 3 yıldır ve kullandığımız veri seti 3 aylıktır. Varistörlerin Bozunum ProsesleriZnO varistörlerde görülen değişik bozunum mekanizmalarını inceledik. Varistör voltajı Vv'nin değişik stres seviyelerinde nasıl değiştiğini modelledik. Bu amaç için, değişik AC akımlar kullanarak hızlandırılmış testler uyguladık ve Vv değerlerini ölçtük. Literatürdeki genel kanının aksine sadece düşen Vv değerleri değil, yükselen Vv değerleri de gözlemledik.

| ||||||||||||||||||||||||||||||||||||||||

Analog Devre Tasarımı | |||||||||||||||

Pozitif GeribeslemeGeleneksel olarak analog devreler pozitif geribesleme çevrimleri içermemelidirler. Aykırı gözükse de, biz bu çalışmada akım kuvvetlendiricilerin giriş empedanslarını pozitif geribesleme kullanarak başarıyla iyileştirdik. Ek olarak yeni bir tamamen farksal akım kuvvetlendirici devresi önerdik ve bu devreyi filtre uygulamalarında test ettik.

| |||||||||||||||

Ayrık Matematik | |||||||||||||

"Self Duality" ProblemiIDNF (irredundant disjuntive normal form) formundaki monoton bir Boolean fonksiyonun self-dual olup olmadığının zaman karmaşıklığında belirlenmesi, matematikte çözülememiş önemli problemlerden biridir. Bu çalışma bu ünlü problem üzerinedir. Biz bu çalışmada IDNF formundaki monoton Boolean fonksiyonların değişken sayısının çarpım (disjunct) sayısından fazla olamayacağını gösterdik. Ayrıca n sayıda çarpım ve n sayıda değişken içeren IDNF formundaki monoton Boolean fonksiyonların, self-dual olup olmadığını bulan bir algoritma geliştirdik. Algoritmanın zaman karmaşıklığı O(n^3)'dür.

| |||||||||||||